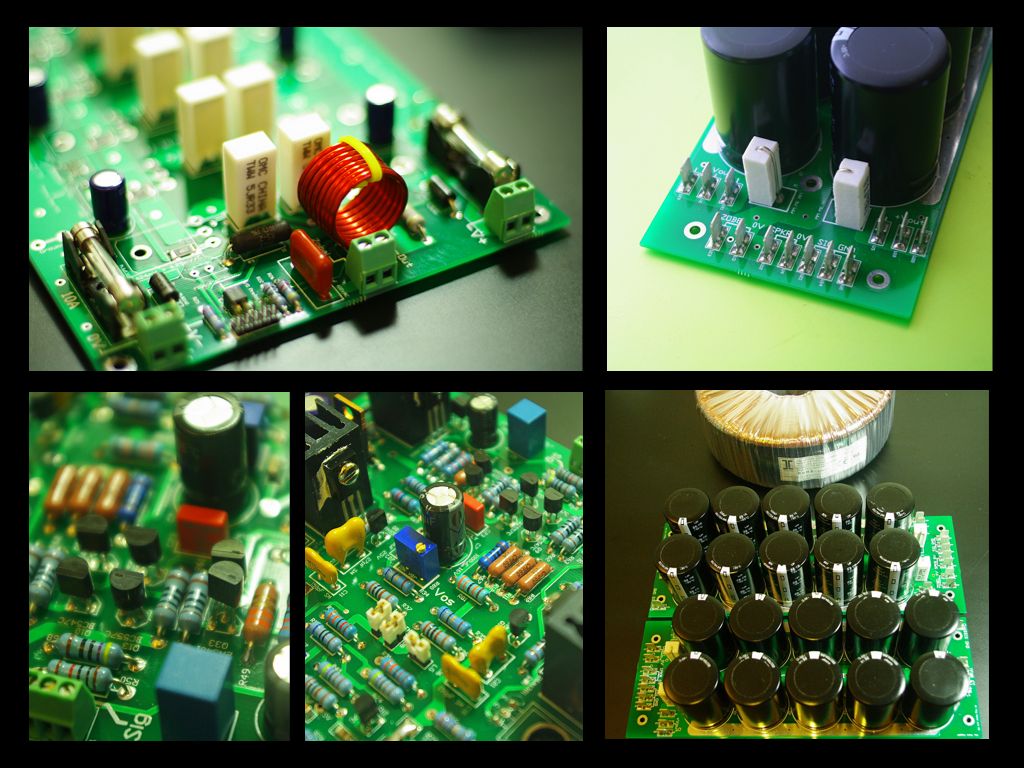

The e-Amp is a 180 Watt RMS (very conservatively rated into 8 Ω ) fully balanced symmetrical (‘FBS’) amplifier featuring an emitter follower triple (EFT) bipolar output stage and beta enhanced VAS stage.

The amplifier can be configured using jumpers for TMC (Transitional Miller Compensation) or straight Miller compensation (MC). The VAS can be lightly loaded to reduce the overall loop gain, but increase the open loop -3 dB bandwidth to 40 kHz also using a jumper. I have called this compensation option ‘Wide Band’ or WB. This allows four compensation schemes to be selected – MC, TMC, WB-MC and WB-TMC. With the e-Amp, by simply inserting or removing a few jumpers it can be flipped from one compensation design another – how it is ultimately tuned, and how it sounds, is up to personal choice.

A microprocessor based protection board takes care of transformer in-rush current limiting at power-up, speaker muting (unusually, using low Rds(on) Trench mosfets), over temperature, DC offsets and output short current protection.

Subjectively the e-Amp produces great imaging, a very smooth, open mid and top end with plenty of bass depth and slam. I personally doubt you could ask for anything more from a power amplifier.

I hope you enjoy reading about the Ovation e-Amp as much as I enjoyed designing, constructing and writing about it.

Here is a .pdf copy of the e-Amp article giving a detailed circuit description with a design discussion covering topology, device technology selection and compensation design (circa 60 pages and 10MB)

__________________________________________________________________________________________________________________________________________

1.0 The e-Amp: A Design Discussion

________________________________________________________________________________________________________________

Although the relationships between key circuit performance parameters are well understood, there is no universal approach or methodology to designing audio amplifiers. You either get taught in engineering school how do it in very general terms, you stick with it and adapt it over time, or you work out your own methodology. Of course, there are now some very good books on the specific subject as well. I use LTSpice very extensively in the design process, since even though you can calculate the required component values to quickly arrive at the initial 1st round nominal values, there is a lot of fine tuning required to get a really good, high-performance design, and that’s even before we start to think about the critical PCB layout and wiring issues. To be sure, what is seen in the circuit model on a computer does not always reflect what is measured or observed on the prototype in the detail, but its close enough to help understand what’s going on in the prototype, and to make sensible tweaks. A major reason for the discrepancy is to do with the accuracy of the models in the simulator to prototype direction, but there are also problems going from the prototype to the model because the prototype real world components with parametric spreads and parasitics (e.g. capacitors, trace inductances and so on) result in behaviour you don’t see at first on your computer, and a typical example is the behaviour of EF triples and cascodes in the presence of PCB trace inductance. Further, there are a few cases where modelling and simulation are problematic, a good example being the FBS topology with mirror loaded LTP (to be discussed a bit further on), which simulates perfectly, but is not DC stable in the real world, rendering it useless in a practical amplifier without some form of VAS DC common mode current control circuit.

1.1 e-Amp Topology: ‘Fully Balanced Symmetrical’ (FBS)

The choice facing the designer of any power voltage feedback amplifier is to go with either a Lin (so called because it was HC Lin of Bell Labs who first proposed the topology in the 1950’s) or FBS topology or some derivative (and there are many) of either. Like the feedback debate, there are those that swear by the Lin topology (popularized by Douglas Self who used it as the demonstrator of his now famous ‘blameless’ amplifier concept) and others that say the FBS can do no wrong. The criticisms from some quarters leveled at the Lin topology stem from the fact that the VAS is not symmetrical and therefore the drive to the output stage is not symmetrical since you have a buffered common emitter stage usually loaded with a current source. The common emitter VAS amplifier can provide substantial currents into the output stage, but the current source limits the drive on the other half of the waveform. As a result, the slew rate (SR) is also not symmetrical, and when Self’s efforts to mitigate this problem are studied, one quickly concludes it is a hopeless cause. Balanced designs suffer none of these drawbacks, offer an additional 6 dB of loop gain, and neatly cancel 2nd harmonic distortion, although some practitioners don’t like this, citing the resultant missing, or lower level, even order harmonic distortion spectra as a negative influence on amplifier sound. There are well known techniques to convert a standard single ended LTP to a balanced drive VAS in which the drive and slew rates are symmetrical. The earliest single ended LTP input to balanced drive VAS I have been able to identify was in Bart Locanthi’s design from 1966 while he was at JBL. Subsequently this was used to good effect by a number of manufacturers, and popularized by Hitachi Semiconductor in their mosfet applications data handbook from the very early 1980s, but I don’t know if they got it from Locanthi, or if it was developed independently. Robert Cordell used a standard single ended LTP to balanced VAS stage topology in his amplifier with mosfet output and error correction, also from the early 1980s. In the FBS topology, originally developed by John Curl, and his subsequent derivative utilizing a folded cascode, SR’s and drive to the output stage is symmetrical and VAS output current drive capability is substantial. However, the FBS small signal stages are generally more complex, and compared to the Lin topology, there is a $ cost penalty (albeit small) and the PCB layout also takes a bit more effort. The Lin topology is simpler, lower cost and still achieves remarkably good results as evidenced by Self’s work. In terms of output stage drive capability, if one uses an EF3 or CFP output stage, the drive issues with the Lin can be reduced substantially, though you cannot readily overcome the differences in positive and negative SR’s. Given some of the shortcomings of the Lin, and I have to say my positive experience with the FBS topology in the Ovation 250 amplifier, the FBS was also selected for the e-Amp. The penalty is slightly higher cost and complexity for the small signal components (maybe around $4 on a one off like this), but I think for a high performance amplifier this is a small price to pay for symmetrical drive of the output stage and an additional 6 dB of open loop gain. I would add at this point that if designing an amplifier for high volume commercial applications, the Lin topology would be my first choice because of its simplicity and cost effectiveness. But, like the Ovation 250, the Ovation e-Amp has definitely not been designed to a price point.

1.2 Front End Design

A general discussion about input device technology, Re, SR, Input Overload, Tail Current and Input Filter

JFETs or Bipolar?

Solid state amplifier designers have a choice of 2 basic device technologies for the input stage: bipolar or JFET. Some idiosyncratic designs use mosfets, but I will not cover these here. The gm of JFETs is much lower than un-degenerated bipolar devices, and in VFAs using conventional Cdom compensation, this translates into higher slew rates for a given distortion mechanisms. JFETs can offer improved RFI immunity over un-degenerated bipolar devices, and some designers claim they are more linear than bipolar devices, but this has been contested. They are unmatched in applications requiring high input resistance (great for condenser mic preamps or photo-diode amplifiers for example) and their very low noise current makes them ideal for things like MM cartridges, or any other high impedance sources. These are all very strong points in favour of the JFET. John Curl, the designer of Parasound amplifiers, carved out a name for himself as the foremost proponent of JFET front ends in audio power amplifiers. Nelson Pass, a class A, ultra simple signal path exponent is also a JFET fan, as is Charles Hansen of Ayre. However, JFETs are not without their problems. Firstly, in FBS topology designs, quite some effort is required to match Idss and Vgs vs Id characteristics to minimize distortion and DC offsets. In both JFET and bipolar designs, balance between the LTP two halves is critical for lowest distortion – however matching JFETs is much more difficult because the device parameters are somewhat ‘looser’ than bipolar devices. Discrete designs using this approach will require a servo to correct for both initial offset and temperature drift. Input capacitance in JFETs is high and very non-linear with respect to the gate drain voltage, causing distortion. One way of getting around this is to cascode the diff amp devices so that Vds is fixed. In bipolar designs the front end LTP stages are often cascoded (as is the case with this design) so that small signal, high hFE devices can be used, since high voltage high hFE transistors are not readily available. Cascoding bipolar devices also aids in PSRR and improves linearity by mitigating Cob effects. In JFETs, the lower gm also translates into lower overall open loop gain, if this is an important design goal (some designers prefer lower loop gain), the lower inherent gm is not a problem, but a virtue.

Modern bipolar input power amplifier designs are almost never configured without input stage degeneration – this in order to improve slew rates and avoid the now extremely well understood TIM mechanism. This also immediately mitigates RFI ingress (an objection often raised by designers who prefer JFETs) but the penalty is additional noise contribution from the degeneration resistors – however the levels are low enough so that they are of no concern in a power amplifier. Of course, gm is also lowered, but the designer has a bit more flexibility as to how much. The input capacitance in bipolar devices is lower, and when the degeneration is factored in, linearity easily matches or exceeds JFETs. Input bias currents are of course higher, and if the tail current is high (which is what I tend to do in my designs to enable high SR’s with standard MC), the feedback and bias resistors need to be low to minimize any resultant offset. However, high input capacitances in JFET designs also mean there is a practical upper limit to the feedback resistor values in those designs as well, to say nothing of the noise contribution. Bipolar input stages are much more DC stable than JFET discrete stages – typically on a well designed power amp using high beta devices 10 ~ 15 mV of offset without hFE matching, and temperature drift of under 10 µV/C. This allows the feedback network to be capacitively coupled (more on this point later), and a simple pot adjustment for offset voltage suffices. Unlike JFETs, good small signal bipolar devices are ubiquitous, and devices from the same batch are remarkably well matched – Vbe of <;2 mV and hFE to within 20% is quite typical. Tighter matching by hand is therefore an absolute cinch, and on BC547C/557C you can easily match devices from the same batch to within 2 ~ 3% at hFE = 500+. The golden age of the JFET is long passed, and some of the best devices ever developed for audio (especially Toshiba) have been EOLed (End Of Life – semiconductor industry parlance for end of production and no longer available). There is quite some niche JFET industry in audio sourcing NOS, faking devices and generating ‘vapor ware’ – i.e. promises of matching N and P channel JFETs on roadmaps that never materialize. No doubt, the very fact that these devices are no longer in production has driven up prices and allowed all sorts of magical audio properties to be attributed to them . . .

There are as many bipolar front end solid state amplifiers in the Stereophile ‘A’ grade category as JFET and Tube designs. Clearly, overall execution and technical expertise enables designers to avoid the cons and exploit the pros of their chosen devices to deliver top class results. For all of the reasons outlined above, and like the Ovation 250 design, the Ovation e-Amp also uses an all bipolar front end.

Slew Rate, Tail Current, Front End Overload and Input Filter

In order to avoid TIM, Leach describes succinctly the requirements to ensure that the input overload capability is not exceeded. The input stage must remain operating in its linear region with the maximum expected input signal dynamic both in terms of magnitude and rise/fall time. Linked to this, the LTP tail current must be able to charge and discharge Cdom quickly enough to ensure that the peak differential voltage between the non-inverting and inverting inputs to the amplifier do not exceed the maximum linear operating region of the input stage. If either of these two conditions is not met, TIM can occur.

Fig. 1 shows the model I used to check for input stage overload capability. The tail currents, I1 and I2 along with the value of Re determine the max input voltage input the stage can handle whilst still remaining linear. Because of the resistively loaded LTP’s (and use of Cdom or TMC compensation), I like to run my front end diff amps stage ‘rich’ with a tail current of about 10 mA (so 5 mA per side) and Re at about 100 Ω as this meets a nominal 0.5 V maximum input signal capability while still keeping the loop gain reasonably high. Because the LTP is resistively loaded, under worst case slew conditions when either Q10 or Q13 are turned on hard and providing the maximum amount of current into Cdom (C10 and C11), a large portion of the tail current is still shunted away from charging Cdom through R71 and R72. In mirror loaded LTP’s, all of the tail current under these circumstances is diverted into charging Cdom, so for the same slew rate, you can get away with half the tail current. The second important reason for running the tail current high, as in the Ovation e-Amp front-end configuration, is in order to achieve high slew rates using standard MC. This translates directly into modest input filter requirements (-3 dB circa 350 kHz) which would otherwise have to be set at a much lower cutoff frequency to ensure there would be no transient overload on the input stage. Due to the compensation design on the e-Amp (to be covered more fully later), a low value for Cdom is used (effectively 25 pF), which results in a slew rate of ~ 155 V/ µs (front end filter disabled). This high slew rate is as a direct result of the high tail current and heavy front end degeneration. Fig 2 shows the output of the model where the input voltage is plotted against the LTP collector currents. The linear range is about ±0.6 V. For higher values of Rem and/or tail current, the input linear operating range increases, but this has to be paid for with a reduction in gm.

;

If this difference voltage exceeds the linear input operating voltage as shown in Fig. 2 (which is just under ±0.6 V), the amplifier cannot be guaranteed free of TIM distortion. Fig. 3 plots the error signal as the delta between the non-inverting input and the inverting input. To simulate this error plot, I fed in a square wave of 25 kHz at ± 1 V pk-pk with a rise time of 100 ns. This is an implausibly fast rise and fall time, but clearly shows the absolute limits of the front end overload capability. If the input stage saturates, there is no feedback – the amplifier is running open loop until the loop recovers. As a result, the output it is likely to end up stuck at one of the supply rails until the loop can gain control again – a very messy situation indeed. However, the cure is simple – either lower the input filter cut off frequency and/or reduce the input stage gm by increasing Re until the difference voltage falls below the maximum linear operating range per Fig. 2.

The front end design and value selected for Cdom therefore ensures that the e-Amp will never run into TIM. Fig. 3 shows the result with no input filter (capacitor value set to 0 pF) and the peak error signal (red trace) is >; 1.5 V. With the Input filter -3 dB cut-off set to 720 kHz, the peak error signal is the lower red trace at about 0.8 peak, while with a 2 µs rise/fall time signal (far more realistic), the peak error signal is 0.3 V – well within the overload capability of the front end. Connecting each channel of a wideband dual channel scope to the inverting and non-inverting input and subtracting the two will directly display the difference waveform and something very similar to that which can be seen in Fig 6. Use a fast rise time square wave input signal for this test – 100 ns is about right – with the front-end filter in situ.

;

In the final design, I lowered the input -3 dB cut off frequency to circa 350 kHz (R68 and C24) as a precaution against RF ingress.

The front end design goals can be summarized as follows:-

1. Ensure that under absolute maximum input drive conditions (i.e., just prior to clipping) the input stage remains linear, as shown in Fig 2 and Fig 3. Use 2 µs rise/fall times for this design step. Increase RE and/or the LTP tail current to ensure this condition is met. Do not provide any more headroom on the front end stage than is necessary, since this has to be paid for by a reduction in loop gain and ultimately, increased distortion.

2. For conventionally Miller Compensated configurations like the e-Amp, run the LTP current high (so 5 ~ 10 mA) in resistively loaded designs to ensure high slew rates and sufficient current to charge and discharge Cdom whilst at the same time providing the current demanded by the LTP collector load resistors.

3. With regard to the input filter, adjust the cut off frequency on the final prototype by looking at the output into an 8 Ω load, and making sure there is no overshoot, being careful not to be too aggressive. An input filter -3 dB of between 300 and 500 kHz is about right for design like the e-Amp. For this design step, use a fast rise time of about 100 ns.

4. Cdom, Re, tail current and the input filter are selected based on a set of tradeoff’s which in turn are highly dependent upon output device Ft.

1.3 LTP Current Source

I spent some time deciding whether to go for active current sources or to use the legacy technique (Marshal Leach and Bart Locanthi designs are good examples) which is to derive the LTP tail currents from a Zener + resistor reference. For the active current sources, one can use the classic transistor+ diode reference, the two back-to-back transistor variant or even a current mirror, where the attraction is that a single resistor can set both +ve and –ve tail currents, albeit with some additional complexity over the other options.

; |

Figure 4 details the options looked at and from left to right they are an ideal theoretical current source with infinite output impedance (for reference), the standard Vref based current source, the popular two transistor type and finally, the Zener derived source. On the output side of the LTP’s (i.e. the diff amp collector load resistors) all of the current sources perform well in terms of +ve supply rejection (see Fig. 5). However, the Zener reference rejection is a little worse at lower frequencies at -147 dB vs 154 dB for the active types and the theoretically perfect current source. The major limitation of the +ve supply rejection is due to the coupling of the +ve rail noise signal through to the bases of the LTP transistors via Cob. Here we see that one of the benefits of cascoding the LTP transistors is to reduce this effect and improve PSRR, although at -126 dB there may be a temptation to concede that it is good enough without it.

Fig. 6 details the –ve rail rejection performance. The green trace is the ideal theoretical current source which is the reference. In both the active types, -ve rail rejection performance falls off (i.e. stops improving) between about 10 Hz and 200 Hz, whilst the Zener derived reference only levels off at 20 kHz and remains considerably better than the other practical options right up to the simulated limit of 10MHz. On the active types, you can cascode the current source transistor, or use a three transistor variant, to get better performance, but the Zener reference performance still cannot be matched.

In Figure 6 above the green trace is the reference based on an ideal current source, dark blue and red the active current sources, and the light blue trace is the Zener + resistor source.

On the e-Amp I ended up going with the two transistor variant (3rd from left in Fig 4) – its performance is on par with the other active designs, its well tried and tested. The Zener reference offers advantages at HF that are clearly evident from the simulation above, but you then have to worry about matching the diodes, and using some big decoupling and filtering capacitors. During prototype development, I consistently got readings across the 1% current sense resistors (R44 and R47 in the e-Amp circuit diagram) of within 2 mV of each other – a 0.6% current source match withoutany selection. This is considerably better than any of the other current source options.

1.4 LTP Load Options

For good performance, the tail current must be shared equally between the two transistors in each LTP (same applies to single ended designs as well). Simulation shows that only a small imbalance can lead to appreciable distortion. Traditionally, audio power amplifier designers have used either resistive load or a current mirror. With a current mirror, you get very good balancing between the transistors in the LTP pair and very high gain. Additionally, as discussed in section 1.2, the SR is doubled over that of resistive loading because all of the input stage tail current can be steered to charge Cdom – none of it is wasted flowing into the collector resistive load. On the face of it, a current mirror load looks like a great solution – and it is on single ended designs like the Lin. However, in the FBS topology, current mirror LTP loads are not DC stable and the amplifier output drifts towards one of the supply rails and remains locked up there – a conventional DC servo won’t help either – and as a result, you have to add a common mode current loop (CMCL) balancing circuit to keep the amplifier output centered.

Further complications with the mirror load are that the amplifier loop gain is much higher and the designer has to wrestle with additional work on amplifier recovery after overload (clipping).

The resistive load LTP was chosen for the e-Amp:- it is simple, there are no DC balance issues, ‘sticky rail’ occurs only in the VAS stage and as we will see a bit later, is easily remedied – and distortion performance is still outstanding. Regarding the requirement to balance tail current, this is set by the input voltage required by the VAS buffer and VAS output transistor Vbe’s plus the voltage drop across the VAS emitter degeneration resistor. The easiest way to do this in practice is to calculate the initial resistor value, check it on a simulator and then tweak the final LTP collector load resistor on the prototype for lowest distortion. The process is simply to take 2 Vbe (since the VAS uses a two transistor follower configuration), allow for a further circa 1 ~ 1.5 V drop across the VAS amplifier emitter degeneration resistor (this is R27 and R69 in the e-Amp circuit diagram) giving around 3 V. The load resistor is then calculated based on 0.5 x the LTP tail current which is 5 mA. In the e-Amp this gives a collector load resistor value of 680 Ω. In the final design, I checked the value to ensure good balance and thus lowest distortion. This value will repeatedly give the lowest distortion across any number of amplifier replicas. Of course, a mirror load with well matched transistors will give better amplifier to amplifier LTP current balancing, but this comes at the expense of the CM balance issues discussed above. Separately, the other aspect investigated on the e-Amp was the effect of unbalanced currents between the two LTPs. Differences of up to 5% have only a minute effect on distortion – in the order of 2 ~ 3ppm. It is the balance between each half of the individual LTPs that is critical for low distortion, and this of course applies to both single ended and FBS topologies

1.5 LTP Load Options

For good performance, the tail current must be shared equally between the two transistors in each LTP (same applies to single ended designs as well). Simulation shows that only a small imbalance can lead to appreciable distortion. Traditionally, audio power amplifier designers have used either resistive load or a current mirror. With a current mirror, you get very good balancing between the transistors in the LTP pair and very high gain. Additionally, as discussed in section 7.2, the SR is doubled over that of resistive loading because all of the input stage tail current can be steered to charge Cdom – none of it is wasted flowing into the collector resistive load (see OR and OR in Fig 10). On the face of it, a current mirror load looks like a great solution – and it is on single ended designs like the Lin. However, in the FBS topology, current mirror LTP loads are not DC stable and the amplifier output drifts towards one of the supply rails and remains locked up there – a conventional DC servo won’t help either – and as a result, you have to add a common mode current loop (CMCL) balancing circuit to keep the amplifier output centered.

Further complications with the mirror load are that the amplifier loop gain is much higher and the designer has to wrestle with additional work on amplifier recovery after overload (clipping).

The resistive load LTP was chosen for the e-Amp:- it is simple, there are no DC balance issues, ‘sticky rail’ occurs only in the VAS stage and as we will see a bit later, is easily remedied – and distortion performance is still outstanding. Regarding the requirement to balance tail current, this is set by the input voltage required by the VAS buffer and VAS output transistor Vbe’s plus the voltage drop across the VAS emitter degeneration resistor. The easiest way to do this in practice is to calculate the initial resistor value, check it on a simulator and then tweak the final LTP collector load resistor on the prototype for lowest distortion. The process is simply to take 2 Vbe (since the VAS uses a two transistor follower configuration), allow for a further circa 1 ~ 1.5 V drop across the VAS amplifier emitter degeneration resistor (this is R27 and R69 in the circuit diagram) giving around 3 V. The load resistor is then calculated based on 0.5 x the LTP tail current which is 5 mA. In the e-Amp this gives a collector load resistor value of 680 Ω. In the final design, I checked the value to ensure good balance and thus lowest distortion. This value will repeatedly give the lowest distortion across any number of amplifier replicas. Of course, a mirror load with well matched transistors will give better amplifier to amplifier LTP current balancing, but this comes at the expense of the CM balance issues discussed above. Separately, the other aspect investigated on the e-Amp was the effect of unbalanced currents between the two LTPs. Differences of up to 5% have only a minute effect on distortion – in the order of 2 ~ 3ppm. It is the balance between each half of the individual LTPs that is critical for low distortion, and this of course applies to both single ended and FBS topologies.

1.6 Feedback Network Coupling

There is a lot of commentary on the web (and in books) about the impact of electrolytic capacitors on amplifier sound and feedback network capacitive coupling. When you pass an audio signal through a suitably sized, quality electrolytic, the AP distortion analyzer shows zero (0) distortion – which, as Self points out in ‘Small Signal Analog Design’ intuitively it should do because it is a short at AC. DA and DF are usually put forward as having detrimental sonic impact, but no concrete evidence to this effect has been shown. The usual solution to get around using an electrolytic capacitor is to use an opamp based servo. However, servo’s are not without their problems, and one has to question whether or not the additional complexity really does bring real sonic benefits. Cordell has pointed out that servos are inside the amplifier feedback loop (as is the coupling cap), and this could also impart a sonic signature. Further, under overload conditions (severe clipping), or situations where there is a lot of very low frequency program material, servos can misbehave, and some sort of DC offset protection is needed for back-up. For this design, I capacitively coupled the feedback network using C7 and C23 to the inverting input of the amplifier. C7 is a large 1000 µF 16 V electrolytic device which is deliberately oversized in order to get around low frequency electrolytic distortion – a problem Cyril Bateman documented in the 1980’s. Provided you keep the AC voltage across an electrolytic below 40 or 50mV, this form of distortion can be eliminated. At HF (so ~ 1 MHz and above), the construction and lead inductance of electrolytic capacitors can cause impedance peaking, which will cause a dip in gain, and this is addressed by C23, a 0.1 µF poly capacitor which simply bypasses the electrolytic. The input transistors are matched for hfe to within 10% and this gave offsets of <;5 mV in two prototypes and in the two final boards. This design does not use a servo and therefore provides output offset adjustment facility by means of R80. Offset drift due to shifts in temperature from c. 25 ℃ to 65 ℃ is less than 1 mV and therefore well below any level that need be of concern.

1.7 The VAS (or more correctly, the TIS or Trans Impedance Stage)

In a conventional Miller Compensated (MC) voltage feedback amplifier, the VAS is in the form of an integrator, with the integrator capacitor formed by Cdom, and the input current provided from the LTP stage collector current. In the closed loop condition, the VAS stage thus has a critical task in converting what is a small signal current of a few micro amps (closed loop condition with normal program material) into a voltage that may swing 100 Vpk-pk or more on a reasonably high power amplifier.

Critical design goals for any VFA VAS can be summarized as follows:-

- Convert small input currents from the front end LTP stage into large output voltages – this is therefore a high gain stage

- Highly linear – closed loop input LTP and VAS distortion should be in low single digit ppm range

- Provide adequate current drive to the output stages – the VAS standing current should therefore be much higher than the expected typical drive current to the output stages, including the usual buffer under worst-case conditions. It goes without saying then that this must be operated well into the class A region under allload conditions

- Swing to within a few volts of the supply rails ideally – so, maximize the potential power from the supply rails

- No ‘rail sticking’ – come out of clipping cleanly and with no parasitics

- Be tolerant of supply rail noise

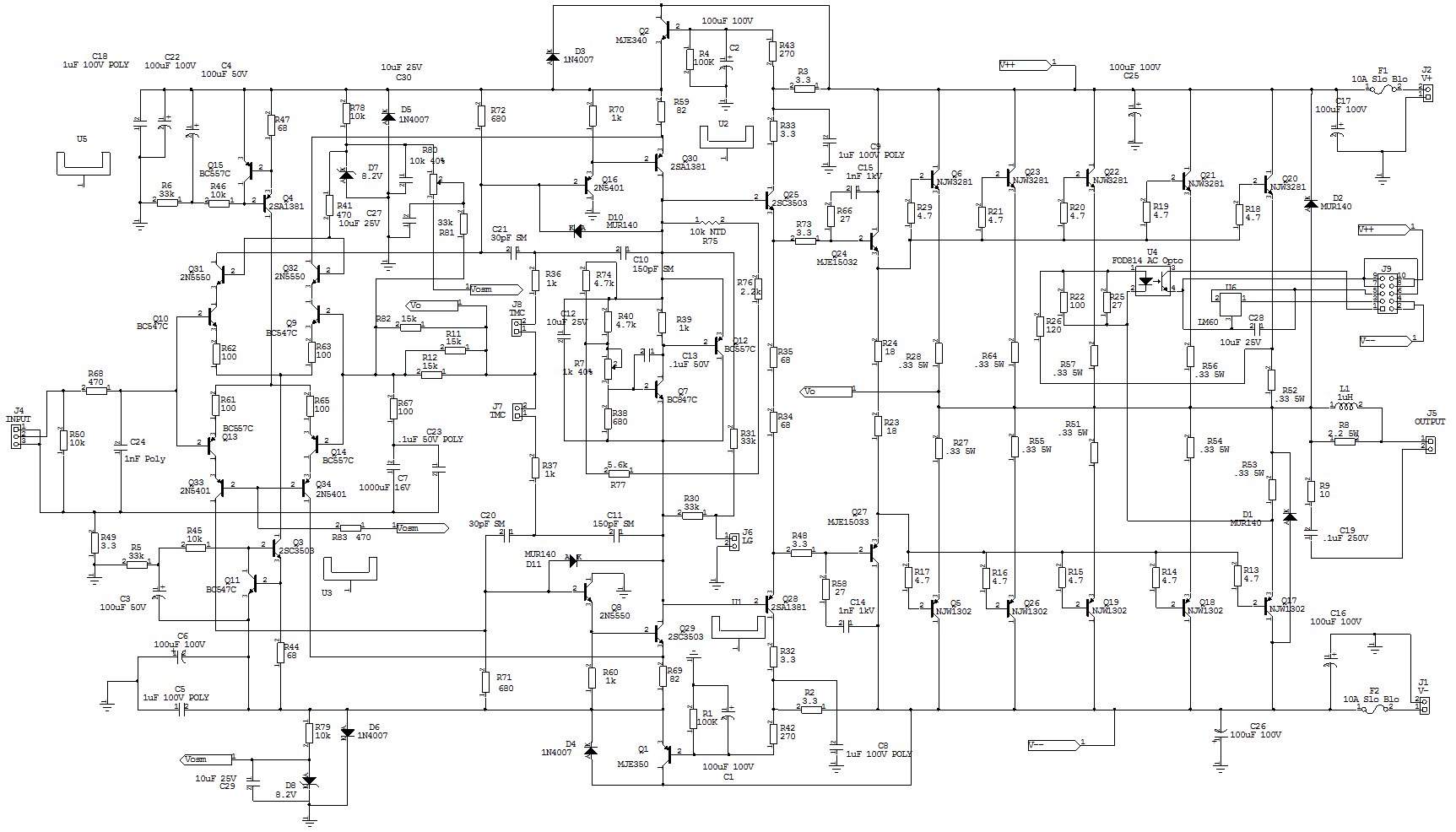

For a VFA, there are many VAS variants but I will stick to conventional options which are the common emitter, Hawksford, cascode and folded cascode. It is important that the VAS local loop gain (i.e. the amplification stage enclosed by Cdom) is high in order to ensure maximum linearity and for this reason the VAS (Q29 and Q30 in the e-Amp circuit diagram) transistors are preceded by ‘beta enhancement’ transistors Q8 and Q16. Without these transistors, the LF open loop gain (when the amp is configured for conventional Miller compensation) is reduced by about 12 dB (from 83 dB to 71 dB), and this has an important impact on the distortion performance of the amplifier across all frequencies.

The collector output of the VAS can either drive the Vbe multiplier directly or use some form of cascode. Cascoding (See Fig 10) is usually used to enable the use of low voltage, high hfe small signal transistors for the VAS amplifier. Cascoding also increases the local VAS loop gain. It is very important that the VAS amplifier transistor, or if a cascode is being used the cascode transistor, has low Cob – and this means in the 2 pF to 3 pF region. The base collector voltage modulates Cob as it swings with the applied input signal, and this is a significant source of distortion in the VAS. Cascode transistors are typically biased at about 3 ~ 5 volts off their associated rails as shown in Fig 7. In general, the approach shown in Fig 7 is sufficient (20 ppm ~ 30 ppm open loop distortion at 20 kHz) although the Fig 9 variant will show about half that due to the reduction of Early effect in Q19.

Another interesting VAS design, is the Hawksford Cascode shown in Fig 8, which achieves reductions in stage distortion an order of magnitude lower than conventional designs whether cascoded or not. In the Hawksford cascode, the cascode base current (an error term) is cancelled by drawing the base current through the emitter degeneration resistor (R27 in Fig 8) and returning it to the collector current of the same transistor (also known as ‘re-circulating’).

;

In the Ovation e-Amp, I chose to use a conventional VAS structure as shown in Fig 7. Since no cascoding is involved, the output voltage swing is maximized – no auxiliary boost supply is required for the front end which is often required with cascode VAS stages (and often seen on mosfet amplifiers to meet the higher Vgs threshold). In simulation, the e-Amp VAS stage + pre-driver will swing 200 Ω load to 100 Vpk to pk at 20 kHz with less than 0.2% distortion, and with a load of 10 k, the figure is in the region of 6 ppm. Given the simplicity, this is good performance indeed.

Due to the high LTP current of 10 mA, when the e-Amp VAS transistor is driven into saturation, there is significant base charge storage in the main VAS transistors, which manifests itself as 3 ~ 4 µs of overhang or ‘stickiness’ on both the positive and negative peaks. At 20 kHz, this results in a truly horrible looking output waveform (see Fig 10 below) and a rapid and dangerous increase in amplifier supply current. The cure here is to use a Baker clamp which shunts base current away from the VAS transistor under overdrive conditions. I used BAV21 diodes (D10 and D11 in Fig. 1) because of their fast switching (c. 50 ns), and very importantly, reverse bias capacitance, which is typically in the region of about 1.2 pF at low reverse voltages. As a result, the Ovation e-Amp comes out of clipping very cleanly and there is little distortion contribution from the modulation of the diode reverse capacitance with VAS output voltage – in the region of low single digit ppm and swamped by other mechanisms in a practical amplifier such as this.

In designs driving mosfet output stages which have high input capacitance, rail sticking exacerbates local parasitic ringing in of the VAS as it exits clipping. This is caused by dynamic short term changes in device parameters (VAS and the mosfets input capacitance) with the changing signal voltage. The amplifier feedback loop tries to correct for this and the result is ringing. Focusing on trying to fix this problem with loop compensation will not work. In all cases, a decent VAS transistor (avoid MJE340/350 types for example) and a Baker clamp will clean things up. Bottom line: sticky rail has to be avoided at all costs.

;

;

;

;

;

;

;

;

;

Figure 10 – ‘Sticky’ Rail – Waveforms Without Baker Clamp (L) and with Baker Clamp (R). Waveforms captured at emitter of the driver stage. Vertical Scale is 50 V/division.

Some designs (e.g. John Curl’s HCA-3500) and the earlier Krell amplifiers used mosfets configured in common source or folded cascode in the VAS stage. These designs will typically not suffer from rail sticking (the base charge storage mechanism in mosfets is different to bipolar devices and related to gate capacitance), and the saturation voltage is very low allowing the full rail of the amplifier to be exploited. Further, the front-end stage can be run at a higher gain (ratio of Rdegen to LTP collector load resistor) because the threshold voltage of the mosfets is higher than bipolars, allowing the use of a higher value LTP load resistor. However, the input capacitance of mosfets is both high and very non-linear; for this reason, it makes more sense to use MIC with these topologies and not MC. Additionally the PSRR in folded cascode designs is not as good as the common source variant, so these designs also benefit from capacitance multiplier techniques in the small signal and VAS supply rails. For now, this probably a topology I will reserve for further investigation in the future.

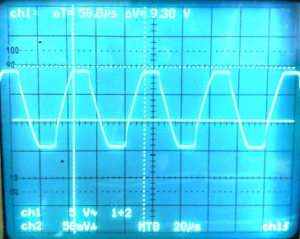

1.8 Keeping Things Quiet – Ripple Eater

The e-Amp employs ripple eater circuits (Q1, Q2, and associated components) to remove rail noise. Although the front-end current sources are heavily filtered and the LTPs are cascoded, if you are really looking for the best possible noise performance, a ripple eater is an invaluable circuit technique. The photo below (Fig 11) shows the supply rail noise at 150 W into 8 Ω and – the upper trace is the mains ripple measured at V+ and superimposed on that the output signal. The bottom trace shows the noise on the supply rails to the front end after the ripple eater and it is well over 30 dB down. When this is coupled to the supply rail rejection afforded by the LTP pairs (through the action of feedback), hum and noise performance is very good – total wideband noise measured at the output is well under 1 mV into 8 Ω.

Note also that the output signal appears as a half wave rectified replica on the supply rails. When playing music, the rails are ‘loaded’ with wideband hash from the rectified output signal (fundamental and harmonics to many hundreds of kHz) and this can feed into the front end and affect performance – and especially so at higher frequencies. Cascoding helps by preventing HF feed through via the collector base capacitance of the LTP pairs, and the e-Amp of course uses both techniques.

Figure 11 – e-Amp Ripple Eater performance

1.8 Output Stage

Mosfets (lateral and vertical types) have some very useful properties, chief amongst them are the lower drive requirements at audio frequencies and lack of secondary breakdown – simple current limiting is ample. Lateral mosfets are much more rugged than bipolar devices and can handle higher peak currents. Mosfets have a much higher Ft than bipolar devices (300 MHz is quite common), so compensation can be easier while more feedback can be applied if that is your persuasion, although you still have to look out for parasitic output stage instability – the solution is the same as for bipolar devices: use a gate stopper (=base stopper for bipolar) but the value is usually about 10x to 20x higher at 30 ~ 100 Ω. Simple buffering of the VAS is all that is required – usually no need for a double or triple follower. But, mosfets need to be reasonably matched if multiple pairs are going to be used in a linear application like a power amplifier. Thermal stability on lateral types is also good, however it usually comes at the expense of quite high drain current (to achieve the zero TC bias point) compared to bipolars.

Self showed that in mosfet output stages, the gm variation in the cross over region is substantially worse than in bipolar designs, and it is very difficult to get anything remotely like smooth signal handoff across the two halves of the output stage – a trick bipolar output stages are much better at. That said, Cordell and a few other designers have made the case that Self’s mosfet models are inaccurate, and the gm cross over discontinuities nothing like as bad in the real world. However, if you want to reduce the cross over non-linearities to manageable levels, then the output quiescent current has to be set quite high – typically 120 mA to 150 mA per pair, and I have seen figures of 200 mA in some designs. On a big amplifier, this might entail 4 pairs totaling out at 600 mA to 800 mA on ± 65 V rails: – thus, you already have an output stage standing dissipation of 78 W to 104 W. This is about twice as much as an equivalent 4 pair bipolar output stage with 0.33 Ω output emitter degeneration resistors, although some designers would argue you may be able to get away with just 3 pairs of mosfets for the same rated power, which is a point I might concede.

Hawksford’s seminal output stage error correction circuit (HEC) addressed mosfet output stage non-linearity, with an early practical demonstration by Robert Cordell. Using this technique, he demonstrated a mosfet amplifier that surpassed bipolar output stage designs in performance terms. More recently, the ‘Pretty Good Poweramp’ or PGP, designed by Edmond Stuart and Ovidiu Popa used HEC and an advanced mirror loaded FBS front end design using nested feedback techniques to demonstrate full power 20 kHz THD of under 1ppm into 8 Ω.

Bipolar devices are easy to apply (although they need VI protection, or very generously designed output stages) and are currently about 30% ~ 40% less expensive per pair. However, for a high quality amp, you do have to factor in the additional driver stage and protection costs, and this means that output stage costs at a systems level probably favour mosfets. If the emitter degeneration resistor on bipolar designs is a reasonable value e.g. 0.27 to 0.33 Ω, matching of output devices, other than ensuring that they are from the same tube, is not required for good current sharing and distortion performance. On two Ovation e-Amp prototypes, I measured a worst case spread across pairs of emitter degeneration resistors of 6 mA and 4 mA – i.e. under 8%. It should noted in the design presented here that the output emitter degeneration resistors are not matched and are 5% types. Modern high power 200 W 15 A bipolar devices have Ft’s up at 30 MHz. While this is not as good as mosfets, it nevertheless facilitates designs with respectable amounts of feedback at 20 kHz – far removed from the days when power device Ft’s were in the order of 2 MHz. Since the hard turn on threshold voltage of bipolar devices is about 3 ~ 4 times lower than mosfets (0.65 V vs. 2 to 2.5 V), higher supply rails to the driver and VAS stages are not required in order to maximize the output device supply rail power delivery. The disadvantages of course are a more complex drive circuit.

The better open loop linearity – a correctly biased EF3 typically produces about 0.1% open loop distortion at mid power loads, rising to about 0.8% at full power – lower output stage quiescent current requirements in Class AB, and easier matching requirements were the reasons I chose to go with a bipolar output stage.

The output stage configuration used is a ‘triple follower’ based on the Locanthi ‘T’ circuit, developed in the 1960’s by Bart Locanthi. It was, and remains, the breakthrough bipolar amplifier output stage configuration and still the best choice if you are looking to maximize the gain bandwidth of a class AB output stage. Like the CFP output configuration however, you still have to take care of emitter follower parasitic oscillation. Topologies like the CFP or Darlington, might respectively give a bit more output swing, or load the VAS a little less, but the ‘T’ is the best overall solution where supply rail voltages are not a restriction, which is the case in the Ovation e-Amp.

For the ‘T’ the designer can employ either an EF2 (i.e. two transistor emitter follower) or an EF3 (three transistor emitter follower, also sometimes just called a ‘triple’ or EFT). I did some Spice simulations that showed that a triple has about an order of magnitude lower distortion in a closed loop amplifier compared to the double. Furthermore, insofar as distortion is concerned, the double shows little tolerance for changes in output load – just the kind of thing to be expected when driving a speaker where the impedance can vary between 2.5 to 16 Ω over the audio band. By contrast, when the amplifier uses the triple output stage, it shows under 10 ppm increase in distortion going from 8 to 4 Ω resistive load, this being mostly due to the increased loading of the VAS stage, especially at higher frequencies.

In the ‘T’ configuration, only the output stage (i.e. the NJW3281 and NJW1302 devices) halves switch in class AB – everything else is operated in class A. Running the pre-drivers and the drivers heavily in class A affords the opportunity to reduce the output distortion arising from switching artifacts that come about as one half of the output stage turns off and the other turns on, and avoid the use of any speed-up capacitors across the pre and driver stage emitter-emitter resistors.

EF3s (and to some extent EF2s) can suffer from high frequency parasitic oscillation, usually in the 10s of MHz range. This oscillation is brought about by the parasitic inductances in the transistor leads and PCB traces. When these inductive components are factored into the practical output circuit of an EF3, they form a Colpitts oscillator structure. Unless specific measures are taken to disassociate the parasitic elements from the active devices, its highly likely that the output stage will be unstable. On the Ovation e-Amp, there are 2 ‘stopper’ networks per positive and negative output halves used for this purpose. I will only cover the top half here. They are R73, R66 and C15 in the base of the driver transistor Q24, and in the collector circuit of Q25, the pre-driver, R3, R33 and C9. These networks effectively swamp (or damp) the lead and trace inductances, breaking the formation of any Colpitts structures, ensuring that the e-Amp EF3 output stage remains stable under all conditions. The additional complexity may be questioned, however, the benefits of the EF3 are much lower load on the VAS stage, improving VAS linearity and effectively raising the open loop gain, and importantly, allowing this amplifier to drive short term loads as low as 2 Ω with less than 50 ppm additional distortion. Few other output stage configurations or device technologies can deliver this type of performance.

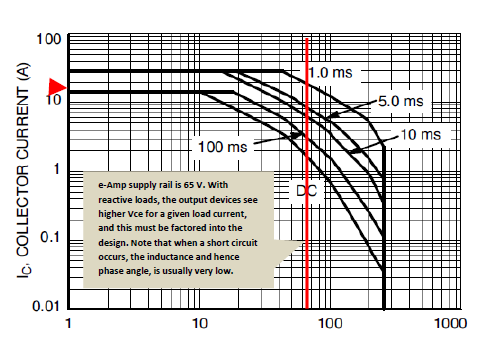

7.9 Output Device Protection: The Tradeoff Game

|

Figure 12 – NJW3281/1302 SOA. The 65 V Vce 1ms Ic capability is 18A (note: rating shown for 25 ℃ – at higher temperatures the curves are derated) |

For commercial and industrial grade applications, protection is necessary, since you can never be sure of the operating environment, and typically will include SOA limiting on bipolar technology output stages, and simple current limiting on mosfet designs. In the Ovation 250, I used 3-slope SOA protection, but later concluded it was too aggressive and intruded on the amplifier sound. On the e-Amp, LTSpice investigation showed that even with very benign protection, driving a 3 Ω 60 degree load (which is an exceedingly heavy worst case scenario), distortion performance was compromised, and to get around this, protection eventually had to be backed off so much it was ineffective, or, the number of output devices had to be increased significantly. In order to be able to handle difficult low impedance and reactive loads (and reduce distortion), the e-Amp employs 5 output devices per rail on ± 65 V rails. In the e-Amp, only simple current limiting is used by measuring the I*R voltage drop across one pair of emitter degen resistors (R52 and R53) using an opto-isolator which feeds into a separate MCU based control board. In a practical hi-fi application, the typical load impedance between about 80 Hz and 1 kHz will be in the 3 ~ 4 Ω region, with dips down to 2 Ω at certain frequencies (speaker model dependent of course). Above about 1 kHz, the impedance starts to increase, while at below about 100 Hz, it increases rapidly as the speaker LF resonance peak is approached. Further below this, the speaker DC coil resistance dominates. 10 A fuses provide back stop protection and these are mounted on the main amplifier PCB. Using this simple protection scheme, the Ovation e-Amp can deliver over 30 A for short periods (50 ms) without any protection circuitry affecting the sonics. In the event of a dead short circuit (so >;>;40 A with the full supply rail across the output devices), the SSR protection scheme on the control board disengages the speaker in under 50 µs, protecting the amplifier. From the SOA curves in Fig. 12, assuming worst-case ± 65 V supply rail (resistive load – a highly reactive load is another matter entirely), the output device capability is bounded by the 1 ms curve above – i.e. about 18 A, or 90 A for the total amplifier with 5 output pairs.

7.10 Vbe Spreader and Thermal Compensation

The Vbe multiplier (bias spreader) circuit consists of two transistors (Q7 is the temperature sensor transistor and Q12 is the spreader shunt transistor in Fig. 1) in a CFP arrangement. With the standard Lin topology (aka Douglas Self’s ‘Blameless’), the VAS standing current is pretty much fixed by the current source load under normal operating conditions. In the Ovation e-Amp and other designs this topology, the VAS standing current can change under heavy load conditions in which the output protection circuit activates. It is important therefore to ensure that the Vbe multiplier remains well regulated so that the output stage standing currents are tightly controlled, hence the requirement for a high gain two transistor circuit. There are other techniques using a single transistor with some slope compensation using a resistor, but these have a higher shunt impedance than the variant used in this design.

Initial set up is accomplished by adjusting the bias potentiometer so that you measure a volt drop across any pair of output emitter resistors (2 x 0.33 Ω = 0.66 Ω) of 52 mV. The figure of 52 mV (or 26 mV across a single emitter resistor) is the optimum emitter resistor volt drop in class AB amplifiers for minimum distortion. Note in this design, that the pre-drivers are also mounted on the main heatsink. In a triple, my approach is to try to keep the output stage devices iso-thermal – more easily said than done in practice (I measured 5 to 7 °C delta between devices using a hand held IR gun type thermometer). In competing designs that mount the pre-drivers on separate heatsinks, care has to be taken where the sensing device is mounted. If for example, the pre-drivers run hot, but you are sensing the output device temperature, you are going to get big shifts in quiescent current during warm up. In this type of layout, you need to sense the pre-driver temperature – both Self and Cordell discuss this in their books.

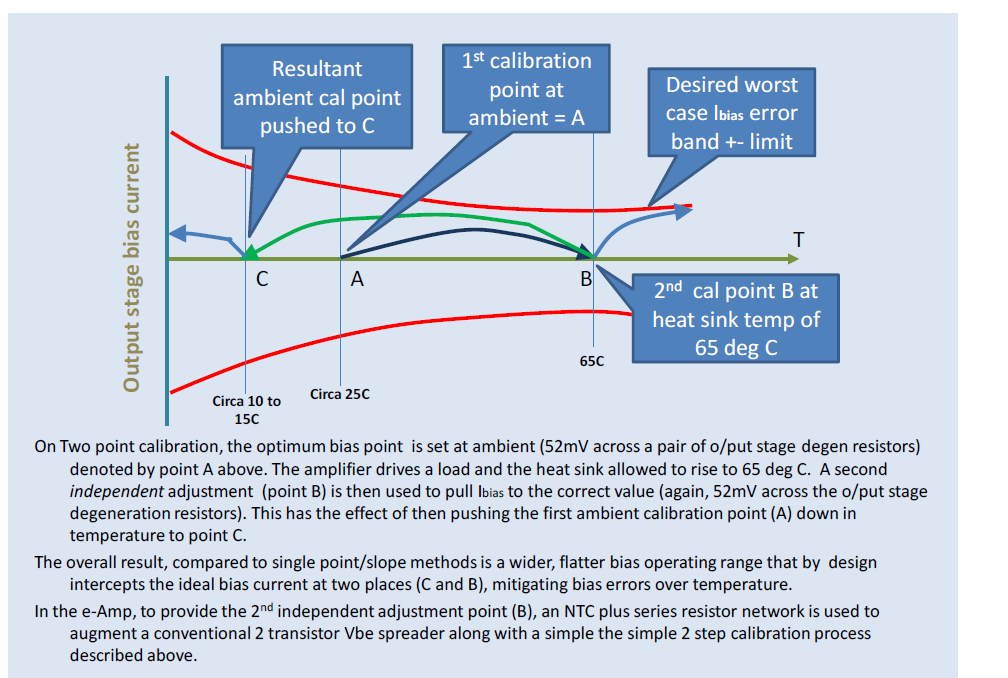

My preferred technique for temperature sensing is to use a small SMD (Q7) device which I closely locate to one of the output device collector leads (easy to do with PCB mount TO247/264 style packages) and then tightly couple this thermally by the application of a small amount of thermal grease over the SMD device and the output device collector lead. Because the SMD device has a low thermal mass, it can respond rapidly to the output device temperature changes, although I have to admit, never as quickly as a co-packaged sensor like the ON NJL1302 and NJL3281 devices (see the data sheet here NJL3281). However, in a triple, the output device Vbe shift with temperature is only 1/3rd of the temp comp problem. The temperature slope of the sensor transistor can be adjusted somewhat by altering the collector current of Q7 between about -1.95 mV per °C and up to about -2.2 mV per °C, which is how I arrived at the 1 k Ω collector load resistor (R39) you see in the circuit (Fig. 1). However, in triples, fast, accurate thermal compensation with just a simple CFP spreader can be difficult and in the Ovation e-Amp, I use a two-point temperature compensation with the aid of a 10 k NTC (R75). R75 is mounted close to one of the output transistor collectors on the component side of the PCB. To calibrate the temperature compensation circuit, R76 + R77 PCB locations are bridged with a 20 k potentiometer – set initially to 10 k – and R7 adjusted for the correct output stage Iq about 1 minute after power up (which is the time it takes to stabilize after switch on). Iq compensation is then accurate to within 10% up until about 50 ℃, after which Iq rapidly diverges (increases) from the ideal value. Once the heatsink temperature reaches 65 ℃, the 20 k potentiometer is adjusted to get the correct Iq level again (52 mV as measured across a pair of output stage 0.33 Ω degeneration resistors). The potentiometer is removed and R76 and R77 are then installed with a total value which is the same as the potentiometer setting. This is a one time calibration cycle and is fixed for the mechanical and electrical design of the amplifier. This calibration method starts out by setting Iq at ambient (assumed to be 22 ~ 27 C) and then readjusting it at a second, higher temperature point (65C). When R76 and R77 are set to the correct value, this moves the original ambient calibration point down in temperature, effectively spreading the two calibration points apart by 10 to 15 °C (the 65°C cal point is fixed and does not move), that employ such that the effective calibration points are 12 to 17 °C (‘adjusted’ ambient) and 65 °C. Using this technique, the output stage Iq variation is better than ± 10 mA around the nominal 78 mA value for all output power levels and ambient temperature conditions after allowing for a few 10s of seconds recovery period after a high power music burst. Temperature compensating EF2s is easy compared to triples, and I have to admit that some of the linearity gains made in moving from an EF2 to and EF3 are lost in the short-term dynamic variation of Iq with program material. However, in designs like this that have moderate loop gains (especially with the loaded VAS and WB-TMC discussed under Compensation later on), you are still well ahead with the triple. The only way to get open loop 0.01% output stage distortion, considering both temperature and load, is to provide some form of error correction. However, HEC as applied to bipolar output stages is problematic, requiring elevated driver supply rails and additional power dissipation. For now, I think the Ovation e-Amp output stage and associated temperature compensation performance for the level of complexity involved is very good. Figures 13 and 14 below summarize the key differences between single and dual point thermal compensation.

The tab and die header temperature of the power transistor are within a few °C of each other and respond quickly to changes in power dissipation. The collector lead (which is part of the header) therefore makes an ideal place to sense temperature.

_________________________________________________________________

2. Feedback and Compensation

There still remains quite some debate within the audio design community on the sonic benefits of wide open loop bandwidth (but lower open loop gain) vs. low open loop bandwidth (but high open loop gain), centering around the causes of PIMD (Phase Inter-Modulation Distortion). And this is before we have even begun to consider Zero Global Feedback vs. Global Feedback debate. With regard to PIMD, the finger of blame has been pointed at the modulation of the loop gain corner frequency in voltage feedback amplifiers. The protagonists have different views on the audibility, the level of PIMD in feedback amplifiers and the cure. Some claim that having the loop gain corner frequency well above 20 kHz may mitigate the problem, since PIM primarily affects signals above the corner frequency. Techniques include the creation of a 2nd nested feedback loop with feedback coming off the VAS itself back to the inverting input (Miller Inclusive Compensation, or MIC), or even resistive feedback around the VAS, as Self has shown. Cordell has written a concise paper (phase_intermodulation_distortion.pdf) on the subject, and in his view, negative feedback all but completely removes the problem.

In the Ovation e-Amp, different compensation modes can be selected by installing or removing PCB jumpers. I originally thought about fitting relays actuated by a front panel switch to accomplish this, but a line has to be drawn somewhere in terms of complexity. The current iteration of this design does not include MIC in the available options, but that will be the subject of a future design. Using simple VAS loading allows loop gain right across the audio band to be reduced, allowing room to experiment more freely on the audibility or not of PIMD, and the general ‘sound’ of the amplifier. Here’s what I target with compensation in my designs:-

- Through the action of feedback, reduce distortion across the audio band

- Ensure adequate gain and phase margins – therefore the amplifier must remain stable into all real world loads.

- The amplifier must display zero oscillation, zero amplifier ringing/overshoot into resistive loads when driving a load without a series output inductor

- Be highly tolerant of capacitive loads covering all practical possibilities when the load is driven through a 1-2 µH inductor in series with the output

- Accept any real world input signal and not suffer from TIM/SID distortion phenomena

For general, simple feedback systems like amplifiers, the easiest and most convenient method to analyze and compensate an amplifier is to use Bode analysis in a simulator. It then becomes a simple matter to adjust values to optimize the performance because as a designer, you are able to ask ‘what if’, then make the change in the simulator, and then observe the results and then try it out on the physical prototype. As part of an iterative design process, this gets one going in the right direction, and the final, optimal compensation component values can quickly be converged upon.

2.1 Standard Miller Compensation (MC)

To kick off, a first guess at Cdom is needed, and that entails some thought about the unity gain bandwidth (UGBW) frequency of the loop. In a typical modern bipolar power audio amplifier with 30 MHz GBW output transistors (the GBW frequency varying markedly with collector current by the way) like the ones used in this design, the UGBW of the loop is set between about 0.5 and 1.5 MHz, the upper value limited by the high frequency poles in the amplifier output stages. For amplifiers using legacy transistors like the 2N3055/2955, the UGBW loop frequency had to be set well below 500 kHz, which amongst other things is why these old designs were doing well at 0.1% THD. The UGBW loop frequency is fixed as part of the design – you cannot simply decide to raise it in order to increase the amount of feedback at lower frequencies because the result will be instability as the HF pole(s) gains rise above unity before the higher UG cross over frequency. Assuming a -20 dB/decade loop roll-off in response, the upper loop UGBW limit is set by the amount of phase shift in the overall system loop, and the lower limit is then fixed by the 20 dB/decade roll-off response. If the -3 dB corner frequency is assumed to be somewhere below 2 ~ 3 kHz (a very reasonable assumption in an amplifier that uses MC like this design), then a GBW of 2 MHz would imply 40 dB of loop gain at 20 kHz, and 60 dB at 2 kHz. Likewise, if the loop UGBW were set at 1 MHz, then the amount of feedback at the frequencies mentioned above would be about 6 dB lower. At this stage, the exact value is not critical because you have to fine tune the compensation design on the bench. To kick this exercise off, the initial UGBW value will be set at 1 MHz – a practical, value for this design. The value of Cdom is then calculated from

Cdom = 1/[2*∏*fx*Acl*2*(Rdegen+re’)]

Where fx = the UGBW frequency – set initially to 1 MHz

Acl = is the closed loop gain magnitude below the -3 db roll off point – i.e. low frequency gain – set to 35

Rdegen is the LTP emitter degeneration resistor which is 100 Ω in this design

re is the internal emitter resistance of the LTP transistors from [0.026/(2*LTP tail current)]

Rdegen is selected independently selected as described in section 7.2 to ensure that the front-end stage remains linear, and for a resistively loaded LTP, assuming a 350 kHz -3 dB input filter, a voltage drop across Rdegen of about 0.5 V is a good value. For a standing LTP current of 5 mA (so half of the 10 mA LTP current source), this gives a value of 100 Ω.

Using the above, we arrive at a value of 30 pF for Cdom. Slew rate (SR) can be independently adjusted by adjusting the LTP tail current (there is also a small influence from re’, but the approximation is good enough for our purposes at the kind of tail currents we are talking about here) and for the values given above, excluding the effect of the front-end filter, this is 155 V/ µs. If the LTP was mirror loaded, the slew rate would be double this figure. The SR can also be increased by increasing Rdegen, but in order to maintain the same UGBW frequency, Cdom would have to be decreased, since there is no point in lowering the UGBW it as this sacrifices OLG. It should again be stressed that the front end filter discussed earlier in section 7.2 forms an important part of the overall compensation of the amplifier – the high slew rate + the 350 kHz front end filter cut off frequency ensure that the e-Amp will never suffer from TIM problems.

Figure 15 – e-Amp MC Loop Gain and Phase Plot

For the e-Amp, I used the Michael Tian et al technique for extracting the loop gain and phase data as given in the examples folder of LTSpiceIV in the file called ‘Loop2’.

Fig. 15 details the standard MC loop gain and phase plot for the e-Amp. The phase margin at the UGBW frequency of 1.3 MHz is 84 degrees (180 – 96), and the gain margin is -13 dB. The recommended minimum phase margin for an audio amplifier is 45 degrees, and gain margin is 6 dB. However, I decided to keep this significant phase and gain margin in hand in order to be able to apply TMC more easily and still have plenty of gain and phase latitude, which will be covered a little further on.

The final test has to be done on the bench where the amplifier must be loaded with an 8 Ω resistor before the output inductorand driven with a 10 kHz square wave of about 2 V pk to pk, with a rise time of about 2 µs (no point in faster rise times, and rise time should also not be much slower than this). The output should not show any signs of overshoot or ringing into a purely resistive load. The next step is to apply a range of capacitive loads across the load resistor connected in the normal fashion after the output inductor, typically from about 100 pF all the way up to 2 µF – half decade values ( so 100 pF, 500 pF, 1 nF, 5 nF etc) will normally be sufficient. The final tests must entail the amplifier driving a 2 to 22 Ω range load with the different parallel capacitance values discussed above, varying the square wave frequency between about 3 kHz and 100 kHz to look for potential problems. Note that when driving a capacitive load, you will get ringing as the output inductor forms a tank circuit with the load capacitance at a frequency of 1/[2*∏*√(LC)] – this ringing has nothing to do with amplifier stability and is quite normal.

On a bipolar output stage power amplifier, loop instability will typically show up as oscillation between about 50 kHz up to 1 MHz Values much beyond this would indicate possible parasitic oscillation, and that is a separate problem from loop stability, and will normally entail a different set of cures. In the tests described above, there must be no indication of any instability.

It is during this bench testing process that the designer can elect to push the UGBW frequency up in order to maximize feedback. In this design, if Cdom were reduced to 10 pF, it would move the UGBW to 3 MHz and the loop gain at 20 kHz from 36 dB to 46 dB. But, with this small value of Cdom, the phase margin rapidly decreases (and here we are definitely on the slippery slope of device to device parametric spreads, layout etc) and the gain margin also declines. If you load an amplifier like this with a worst case real world load, even with the output inductor, the phase margin deteriorates very rapidly. There are techniques, like lead compensation across the feedback resistor, that will allow you to claw back some of the gain and phase margin, but then you have to contend with RF ingress and you still have to deal with component spreads and so forth from unit to unit. What is important is that the final compensation design leaves plenty of leeway for driving capacitive loads. There are too many designs (some published in popular electronics magazines), where in the mistaken notion of chasing the lowest possible distortion, the final result is more often than not a marginally stable amplifier that breaks into oscillation, or rings, with real world loads. I also know from my own amplifier construction experience that stable amplifiers sound better than ones optimized for low distortion at the expense of stability margin. Stability should always take priority over shooting for the lowest distortion.

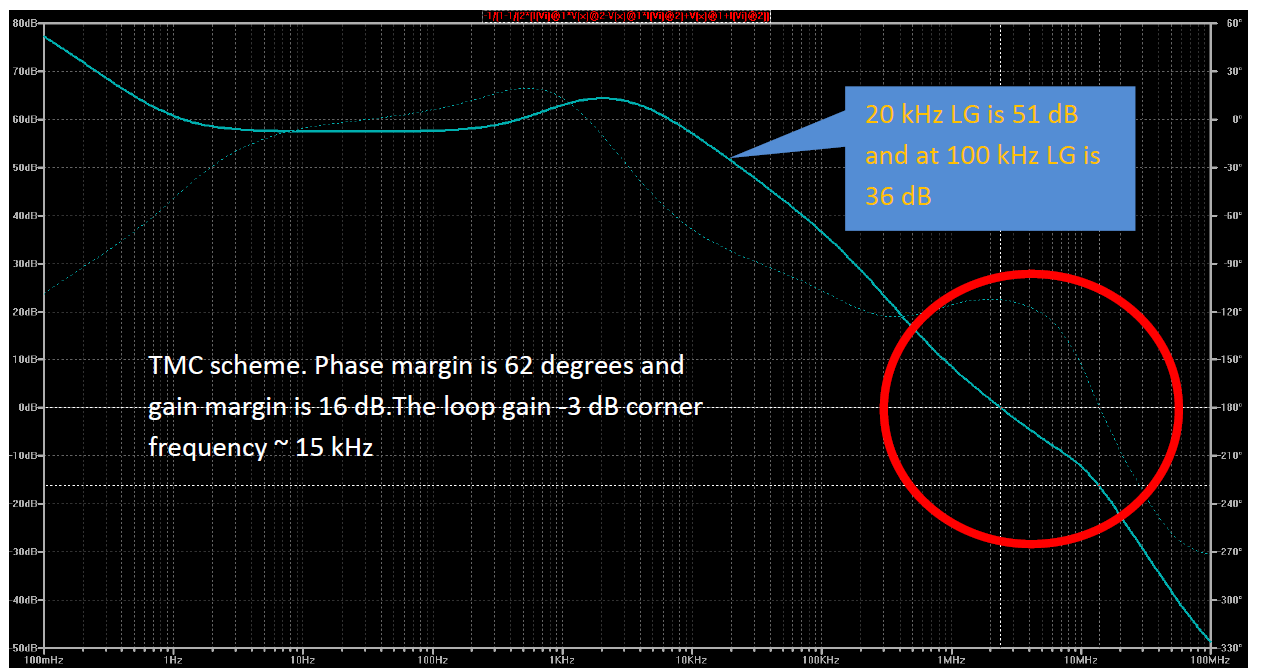

8.2 Transitional Miller Compensation (TMC)

In the e-Amp, invoking TMC requires fitting jumpers J7 and J8 which connect an additional set of capacitors and resistors into the compensation network. TMC works by enclosing the output stage within the Cdom local feedback loop, and then transitioning the output stage out of the Cdom-VAS loop at HF where output stage phase shifts become troublesome. This contrasts markedly with MC, where the output stage is never included in the Cdom-VAS loop, and in order to maintain stability, feedback is actually curtailed (‘thrown away’) at HF to ensure that the output stage poles fall below the unity gain cross over frequency. In TMC, the typical transition frequency depends upon the output devices but a figure of between 500 kHz and 1 MHz appears to give the best results with the output stage devices used in this design. In the Ovation e-Amp, with a 26 degree phase margin impact (and this is why the MC phase margin was left at 84 degrees), TMC improves the available feedback at 20 kHz from 36 dB in the standard MC configuration, to around 51 dB. This delivers a 5x reduction in THD at 20 kHz – a very significant improvement for the cost of 2 resistors and 2 capacitors. I tested TMC extensively on my other design, the Ovation 250, and can confirm that it is very reliable and if implemented correctly with a reasonable transition frequency and does not suffer from any tendencies to oscillate or ring. Fig. 16 shows the TMC loop gain and phase performance.

The next e-Amp compensation configuration to explore is a hybrid ‘Wide Band Feedback’ or WBF+TMC (see Fig. 17 below). Here, TMC is combined with light VAS stage loading to push the loop gain -3 dB point up to about 40 kHz, to ensure the feedback factor (i.e. loop gain) is constant across the audio band. Recall from earlier discussions that some designers believe that PIMD is caused primarily by the loop gain corner frequency lying within the audio band – and for conventional MC on the Ovation e-amp, this is about 2 kHz (see Fig. 15). The corner frequency is modulated by changes in input stage gm as the input signal varies. By loading the VAS (insert jumper J6), the loop gain is flattened, but with the help of the TMC loop, still maintained at a reasonable level, such that at 20 kHz there is 46 dB of feedback. Again, as with the previous two compensation schemes, there is enough gain and phase margin, and the amplifier remains unconditionally stable.

Figure 17 – e-Amp WB TMC Loop Gain and Phase Plot

8.4 Alternative Compensation Strategies

The Ovation e-Amp compensation schemes use Miller, TMC and loop gain reduction (through VAS loading) for loop gain bandwidth spreading and some combinations of these. There are alternative strategies which offer increased slew rates. The e-Amp standard MC slew rate is in the region of 155 V/ µs. Dispensing with Cdom MC and using MIC would allow this to be dramatically increased. With MIC, Cdom is returned not to the VAS stage input, but to the amplifier inverting input, enclosing the input and VAS stages at HF and then enclosing the output stage in a separate, global feedback loop via the normal feedback resistor network. Since the Cdom plus input stage gm integrator structure essential to conventional MC is removed, this breaks the it=CV slew rate limit (i.e. they are ‘non-slewing’), and using this approach, Cordell’s mosfet amplifier from the early eighties featured a SR of c. 300 V/µs. Similarly, John Curl’s HCA-3500 featuring an all JFET complimentary input stage also used MIC to achieve very high SR’s. MIC usually requires some additional compensation of the input stages – typically an RC network across the LTP collector load resistors or mirror, or VAS shunt loading to ground – to ensure stability of the front end stage plus VAS loop.

Still other MC strategies include the (pre) driver stage in the main Cdom loop. I experimented with these approaches and on the simulator, was easily able to achieve single digit ppm distortion levels at full power, but in practice stability was a big issue. On one of the Ovation e-Amp prototypes, I included the pre-drivers in the feedback loop, and got HF burst oscillation between 5 and 8 MHz. The only cure was an additional frequency transition compensation network, and I decided for reasons of practicality, to draw a line in the sand and abandoned the idea. That said, by virtue of the fact that you are able to put about 15 dB more feedback around the output stage at HF, TMC does a really excellent job of reducing overall amplifier distortion without any stability issues.

8.5 Output Inductor and Zobel Network

When an amplifier (and this includes op-amps and discrete small signal amplifiers as well by the way) drives a capacitive load, high frequency poles in the output stage devices that lie above the unity gain cross over frequency (and therefore have gains of <;1) move downward in frequency, such that these poles then end up with gains of >; unity. The additional phase shift therefore taking place before the unity gain cross over frequency, leads to instability or oscillation. Output inductors to ensure unconditional stability on modern amplifiers are in the region of 0.5 to 1 µH, this lower range of inductance values primarily as a result of fast, high Ft output devices and a better understanding of compensation in the general amplifier design community. Output inductors in the region of 0.5 to 1 µH have little sonic effect in the audio band or on the damping factor because at higher frequencies, the speaker cable and cross-over network inductances dominate (straight cable inductance is ~ 1 µH per meter). On a typical audio installation, cabling inductances are as much as 3 ~ 5 µH, and the speaker and cross over network inductances will be many times this value (2 ~ 4 mH), but they are also damped by the speaker coil resistance. Cable, crossover and speaker capacitances can range from a few tens of nF, all the way up to 1 ~ 2 µF for an electrostatic speaker load.

It is quite possible to configure amplifiers to exclude the output inductors, and there are a number of designers of commercial equipment that have taken this approach – for example John Curl (Parasound) and Charles Hansen (Ayre). For this to work reliably, the gain and phase margins have to be sufficient under worst case conditions, or, as in the case of Ayre, the amplifier has to run with zero global feedback. In a feedback design, this might typically entail running at lower loop gains, using high(er) speed output devices like the ones used in the Ovation e-Amp, with a small amount of lead compensation (which can add another 6 dB or more of gain margin if appropriately sized). The e-Amp includes an output inductor of 1 µH. Along with the generous gain and phase margins, this makes the e-Amp an unconditionally stable design – it will therefore drive any capacitive load up to 2 µF in parallel with any resistive load of 2 Ω and higher. The additional gain and phase margin afforded by the output inductor can also be traded for about 6 dB more loop gain, which of course can bring distortion reduction benefits if you choose to do this, but my earlier comments in this regard should be noted. As mentioned before, it is better to err on the side of caution with regard to compensation, and concede some distortion performance in the interests of absolute stability.

A Zobel network – R9 and C19 – is connected between the output rail and the filter capacitor 0 V junction. The Zobel network connected before the output inductor presents decreasing impedance as frequency increases, and therefore partially cancels the inductive load impedance increase of the speaker and associated cable. The net result is that the amplifier load looks essentially resistive. This improves stability and amplifier settling time. Some designs take the Zobel from the speaker side of the inductor, where it can compensate for increasing speaker and cabling impedance at higher frequencies, while I have also seen designs with Zobel networks both before and after the output inductor. To re-iterate the point made earlier, it is important that the Zobel network ground is returned separately to the main filter capacitors 0 V junction directly and not simply tacked onto the local PCB ground return – this to avoid injecting high frequency currents into the local ground which would then couple up onto the supply rails and into the front end small signal chain, causing distortion and possible instability.

3. Protection

________________________________________________________________________________________________________________________________________________

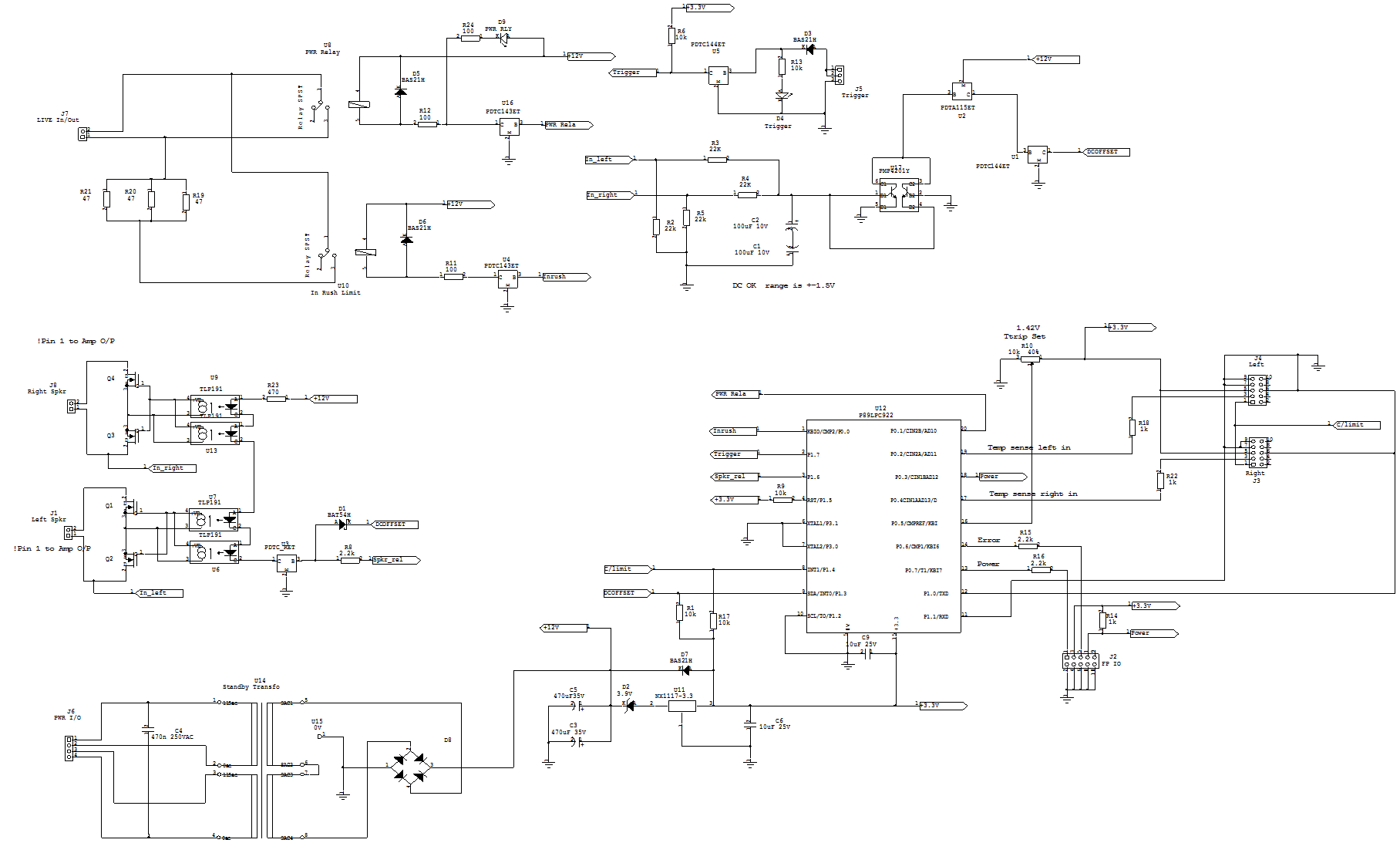

Amplifier protection is provided by separate board based on an 8 bit NXP 89LPC922 MCU (U12 in Fig. 18) and associated circuitry. This covers heatsink over temperature sensing and shutdown, speaker mute, transformer in rush current limiting, output short circuit and DC offset detection and shutdown, and ON/OFF control via a push button switch. Each amplifier board is connected to the controller board via a 10 way IDC ribbon cable (J3 and J4) , while a 3rd ribbon cable (J2) connects to the front panel LED’s (Power which is green and Error which is red) and pushbutton switch.

;

The speaker connections come in via J1 and J8 – note that pin 1 has to be connected to the amplifier output while pin 2 has to go to the speaker HOT side because the amplifier DC detect is taken off pin 1. The speaker muting function is implemented using a solid-state loudspeaker relay (SSLR) with two off back-to-back connected 150 V TO220 Trench FET technology devices (Q1 through Q4) from Fairchild (part # FDP083N15A). These feature a typical Rds (on) of around six mΩ, for a total relay end-to-end resistance of less than 15 mΩ. These devices can handle peak currents when ON of c. 100 A. The mosfets are driven by parallel connected photo-couplers (U6, U7, U9 and U13), which improves the switching speed significantly and this is done in order to keep within the mosfet switch devices SOA – even so, the 1 ms current capability at 70 V is still around 6 A, while the 100 µs capability is 100 A. Therefore, if you switch them quickly at under 100 µs, these devices can make or break enormous load currents. Further, the Rds(on) changes little with currents below about 50 A when the devices are turned on hard (so Vgs is 10 to 12 V) and this translates into very low distortion which I sim’d at about 1 ppm, and AP measurements taken by other designers using a similar topology confirmed these figures. The total end to end SSLR resistance is significantly lower than any readily available electromechanical relay, and the SSLR solution can take some serious abuse – for example like cleanly switching fault currents as high as 40 A in <;200 µs in this specific design. Further, since there is no contact wear out mechanism there are no long-term reliability issues to contend with. Provided the operating envelope remains within the maximum thermal and electrical specifications of the mosfets, these devices can switch these huge fault loads day in and day out, year after year. There are no relays with equal or lower contact resistance that can do that at reasonable cost or similar speed.

The LIVE mains feed to the main power transformer is taken via J7. For power ON/OFF and in-rush (or ‘soft start’) current limiting, standard 16 A Tyco relays are used – unlike the speaker muting function described above, this is where a relay solution is a good fit – and this prevents mains switch-on voltage dips (and mains ECB trips) by limiting the transformer magnetizing in-rush current, as well as limiting the smoothing capacitor initial charge-up currents. U8 and associated circuit handles Power ON/OFF, while U10 takes care of the inrush current (the soft start time is set to about 5 seconds), which is limited by 3 x 7 W 47 Ω resistors in parallel (R19 through R21). Without soft start current limiting, the peak currents through the rectifier and associated wiring can be as high as 250 A and take up to 5 to 10 mains cycles before settling at the normal running peak currents which are in the region of 20 to 30 A in this design.

Heatsink temperature sensing is accomplished with SMD mount LM60 temperature sensors which are located near the collector lead of one of the output devices on each amplifier board and thermally coupled using some silicon grease. The sensor outputs feed into the control board via J3 and J4 pin 3, with pin 5 providing the necessary 3.3 V to power them up. The trip temperature is set to 70 °C by adjusting VR1 on the protection board for a reading of 0.8615 V on pin 14 of the MCU (comparator external reference input). The sensors feed into the comparator inputs pins 19 and 17 on the MCU. 6 °C hysteresis is provided by turning open drain port P1.0 LOW, which in turn pulls the comparator reference down by c. 45 mV via R7. Note that both the temperature sensors and the over current detect opto-isolator circuits on the amplifier boards are completely floating in order to prevent ground loops or any possible noise problems.